**Product data sheet**

### 1. General description

The SSL5261PT is a highly integrated, high-precision dimmable controller with an external MOSFET. It is intended to drive LED lamps in dimmable lighting applications up to 25 W. The SSL5261PT is designed for high power factor, phase-dimmable applications.

The SSL5261PT operates in Boundary Conduction Mode (BCM) with on-time control. It provides a constant output current control with good LED output current accuracy. Adaptive switching frequency gives freedom to choose the inductor, which enables the optimization of inductor size, efficiency and EMI.

The SSL5261PT can start up and operate in switching mode directly from an external resistor without capacitor charge pump supply or auxiliary supply. This feature simplifies the  $V_{CC}$  supply. So, a low-cost off-the-shelf inductor can be used, which provides flexibility in application design.

The SSL5261PT has a separate feedback and current sense input. This input makes the part suitable to be used in buck and buck-boost topologies.

The voltage on the DIM pin regulates the output current by controlling the peak current in the inductor using the feedback from the ISNS input.

### 2. Features and benefits

- Supports most available dimming solutions

- Deep dimming level

- Flicker-free dimming

- Peak dimming control

- Low component count ensuring a compact solution and small, single layer Printed-Circuit Board (PCB) footprint

- Excellent line regulation and load regulation and good LED output current accuracy

- Flexible buck or buck-boost applications

- Efficient BCM operation with:

- Minimal reverse recovery losses in freewheel diode

- ◆ Zero Current Switching (ZCS) and Valley switching for turn-on of switch

- Minimal inductance value and size required

- ◆ High efficiency (up to 91 %)

- Ultra low IC current during operation (< 200 μA)</li>

- Auto-recovery protections:

- UnderVoltage LockOut (UVLO)

- Cycle-by-cycle OverCurrent Protection (OCP)

- Internal OverTemperature Protection (OTP)

- Output OverVoltage Protection (OVP)

- Output Short Protection (OSP)

- Extended IC lifetime

# 3. Applications

■ The SSL5261PT is intended for low-cost, non-isolated dimmable lighting applications that work from single mains voltage.

#### Quick reference data 4.

Table 1. Quick reference data

| Symbol                | Parameter                              | Conditions                                     | Min  | Тур  | Max | Unit |

|-----------------------|----------------------------------------|------------------------------------------------|------|------|-----|------|

| V <sub>CC</sub>       | supply voltage                         | operating range [1]                            | 9.9  | -    | 16  | V    |

| R <sub>DSon</sub>     | on-state                               | source-switch                                  |      |      |     |      |

|                       | resistance                             | T <sub>j</sub> = 25 °C                         | -    | 0.87 | -   | Ω    |

|                       |                                        | T <sub>j</sub> = 125 °C                        | -    | 1.2  | -   | Ω    |

| I <sub>I(SW)</sub>    | input current on pin SW                | duty cycle < 20 %                              | -2   | -    | +2  | А    |

| V <sub>I(SW)</sub>    | input voltage on pin SW                | current limited at 8.8 mA; internal switch-off | -0.4 | -    | +22 | V    |

| V <sub>IO(COMP)</sub> | input/output<br>voltage on pin<br>COMP | operating range in application                 | 2    | -    | 4   | V    |

| V <sub>I(ISNS)</sub>  | input voltage on pin ISNS              | operating range in application                 | 0    | -    | 0.9 | V    |

| $V_{I(FB)}$           | input voltage on pin FB                | operating range in application                 | 0    | -    | 1.8 | V    |

| $V_{I(DIM)}$          | input voltage on pin DIM               | operating range in application                 | 0    | -    | 0.9 | V    |

<sup>[1]</sup> An internal clamp sets the supply voltage. The current into the VCC pin must not exceed the maximum  $I_{VCC}$ value (see Table 4).

# **Ordering information**

Table 2. **Ordering information**

| Type number | Package          |                                          |         |  |  |  |  |

|-------------|------------------|------------------------------------------|---------|--|--|--|--|

|             | Name Description |                                          | Version |  |  |  |  |

| SSL5261PT   | SO8              | plastic surface-mounted package; 8 leads | SOT96-1 |  |  |  |  |

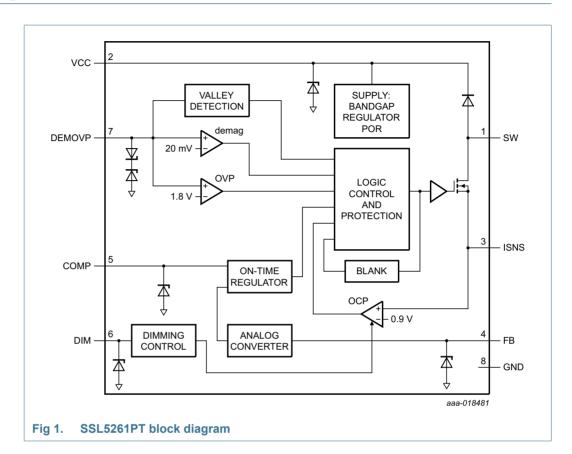

# 6. Block diagram

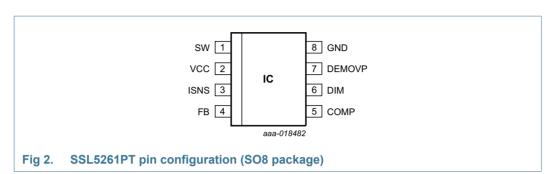

# 7. Pinning information

### 7.1 Pinning

### 7.2 Pin description

Table 3. Pin description

| Symbol | Pin | Description                                                                 |

|--------|-----|-----------------------------------------------------------------------------|

| SW     | 1   | internal source-switch drain                                                |

| VCC    | 2   | supply voltage                                                              |

| ISNS   | 3   | current sense input                                                         |

| FB     | 4   | regulation input                                                            |

| COMP   | 5   | loop compensation to provide stable response                                |

| DIM    | 6   | dimming control input                                                       |

| DEMOVP | 7   | input from LED output for demagnetization timing, valley detection, and OVP |

| GND    | 8   | ground                                                                      |

## 8. Functional description

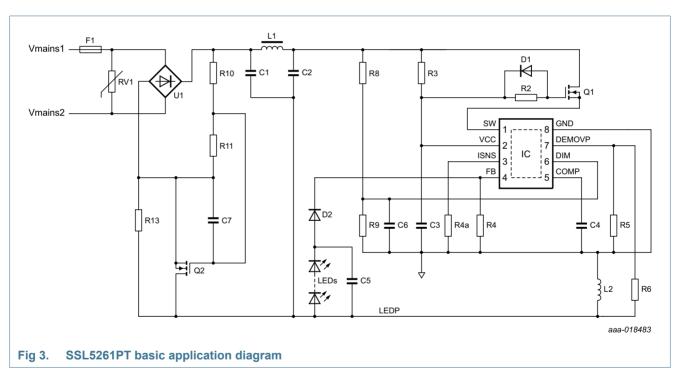

#### 8.1 Converter operation

The converter in the SSL5261PT is a source-switch, BCM, on-time controlled buck or buck-boost system. Figure 3 shows the basic buck-boost application diagram. To save IC supply current, an integrated source-switch topology is used. It enables that even in switching mode only an external resistor is used as supply.

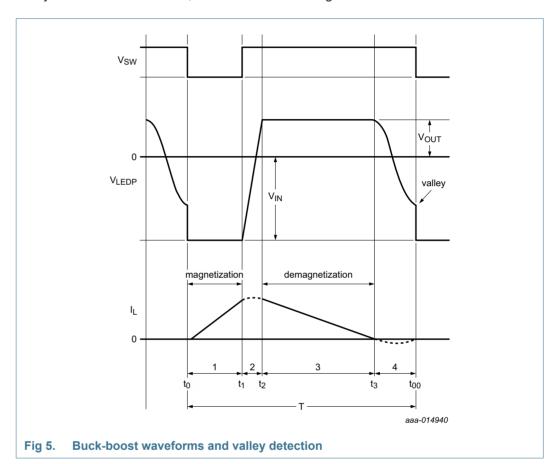

The converter operates at the boundary between Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM). Figure 5 shows the waveforms.

When the internal source-switch is switched on at t0, the inductor current  $I_L$  proportionally to  $V_{in}$  builds up from zero during the source-switch on-time (t0 to t1). Energy is stored in the inductor. When the internal source-switch switches off at t1,  $I_L$  flows through the freewheeling diode and the output capacitor. The inductor current drops proportionally to the  $V_{out}$  value (t2 to t3). When  $I_L$  reaches zero at t3, a new switching cycle is started after a short delay (t3 to t00) from valley detection.

#### 8.2 On-time control

When measuring the inductor current  $I_L$  using sense resistor R4, the on-time is regulated so that the average FB voltage ( $V_{intregd(AV)FB}$ ) is regulated to  $V_{intregd(max)FB}$  (155 mV typical) during the off-time of the main switch. The average output current  $I_{out}$  can be calculated with Equation 1:

$$I_{out} = \frac{V_{intregd(AV)FB}}{R4} \tag{1}$$

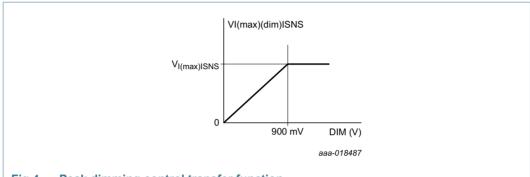

### 8.3 Peak dimming control

When measuring the phase-cut mains voltage using the DIM pin, the DIM voltage modulates the internal OverCurrent Protection (OCP) voltage ( $V_{I(max)(dim)ISNS}$ ) cycle-by-cycle. The regulated maximum current in inductor  $I_{L(max)dim}$  can be calculated with Equation 2:

$$I_{L(max)dim} = \frac{V_{I(max)dim(ISNS)}}{R4a + R_{bond} \times \delta_{swon}}$$

(2)

Fig 4. Peak dimming control transfer function

### 8.4 Valley detection

When  $I_L$  has decreased to zero at t3, the LEDP voltage starts to oscillate around the 0 V level, with amplitude  $V_{OUT}$  and frequency ( $f_{ring}$ ). A special circuit called valley detection is integrated in the SSL5261PT. It senses when the LEDP voltage reaches its lowest level (valley) at the DEMOVP pin. The internal source-switch is switched on again when the valley is detected. As a result, the switch-on switching losses are reduced.

#### 8.5 Start-up current

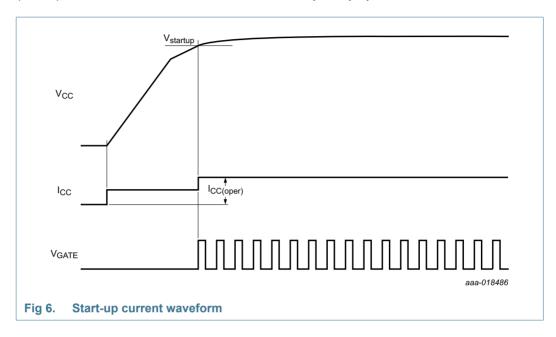

The supply current for the IC is supplied by resistor R3. Just after  $V_{CC}$  reaches the start-up voltage level ( $V_{startup}$ ), the IC draws the operating current ( $I_{CC(oper)}$ ). The internal switch ( $V_{GATE}$ ) starts to drive the external source switch cycle-by-cycle.

### 8.6 Leading-Edge Blanking (LEB)

To prevent false detection of overcurrent, a blanking time following switch-on is implemented. When the internal source-switch turns on, a short current spike can occur because of the capacitive discharge of voltage over the drain and the source. It is disregarded during the LEB time  $(t_{leb})$ .

#### 8.7 Magnetization switching

When the mains voltage is very low, during dimming or around the zero crossings of the mains, the system hardly delivers any energy to the LED. To improve the efficiency, maximum off-time ( $t_{off(max)}$ ) switching limits the switching frequency to < 25 kHz. A peak voltage on the ISNS pin below the  $V_{I(min)ISNS}$  voltage indicates a low mains voltage.

#### 8.8 Protections

The IC incorporates the following protections:

- UnderVoltage LockOut (UVLO)

- Cycle-by-cycle OverCurrent Protection (OCP)

- Internal OverTemperature Protection (OTP)

- Cycle-by-cycle maximum on-time protection

- Output OverVoltage Protection (OVP)

- · Output Short Protection (OSP)

### 8.8.1 UnderVoltage LockOut (UVLO)

When the voltage on the VCC pin drops to below  $V_{th(UVLO)}$ , the IC stops switching. An attempt is made to restart IC when the  $V_{CC} > V_{startup}$ .

#### 8.8.2 Cycle-by-cycle OverCurrent Protection (OCP)

The SSL5261PT contains a built-in peak current detector. It triggers when the voltage at the ISNS pin reaches the peak level  $V_{I(max)ISNS}$ . A resistor connected to the ISNS pin senses the current through the inductor  $I_L$ . When the voltage on DIM pin is higher than  $V_{I(max)ISNS}$ , the maximum current in inductor  $I_{L(max)}$  can be calculated with Equation 3:

$$I_{L(max)} = \frac{V_{I(max)ISNS}}{R4a + R_{bond} \times \delta_{swon}}$$

(3)

#### Where:

- R<sub>bond</sub> is the ISNS bond wire resistance

- $\delta_{\text{swon}}$  is the switch-on duty cycle

The sense circuit is activated after the LEB time ( $t_{leb}$ ). It automatically provides protection for maximum LED current during operation. A propagation delay exists between overcurrent detection and the actual source-switch switch-off. Due to this delay, the actual peak current is slightly higher than the OCP level set by the resistor in series with the ISNS pin.

#### 8.8.3 OverTemperature Protection (OTP)

When the internal OTP function is triggered at IC junction temperature  $T_{pl(IC)}$ , the converter stops switching. The IC resumes switching when the IC temperature drops to below  $T_{pl(IC)rst}$ .

#### 8.8.4 Cycle-by-cycle maximum on-time protection

Measuring the inductor current  $I_L$  using sense resistor  $R_{\text{sense}}$  regulates the on-time. The on-time is limited to a fixed value  $(t_{\text{on}(\text{max})})$ . It protects the system and the IC when the ISNS pin is shorted or the system works at very low mains.

#### 8.8.5 Output OverVoltage Protection (OVP)

Measuring the voltage at the DEMOVP pin during the secondary stroke gives an accurate output OVP. The resistive divider connected between the LEDP node and the DEMOVP pin sets the maximum LED voltage.

An internal counter prevents false OVP detection because of noise on the DEMOVP pin. After three continuous cycles with a DEMOVP pin voltage exceeding the OVP level, OVP is triggered.

OVP triggers a restart sequence: A discharge current  $(I_{CC(dch)})$  is enabled and discharges  $V_{CC}$  to below  $V_{rst(latch)}$ . When  $V_{rst(latch)}$  is reached, the system restarts.

#### 8.8.6 Output Short Protection (OSP)

The converter operates in Discontinuous Conduction Mode (DCM). A new cycle is only started after the previous cycle has ended. Measuring the voltage on the DEMOVP pin detects the end of the cycle. When the DEMOVP pin voltage drops to below the demagnetization level (V<sub>det(demag)</sub>) and a valley is detected, a new cycle starts. The converter regulates the adjusted output current and the on-time is reduced to a safe value by this feedback. The reduced on-time in combination with a very long demagnetization period prevents the converter from any damage or excessive dissipation.

To prevent false demagnetization detection, a blanking time  $(t_{sup(xfmr\_ring)})$  is implemented at the start of the secondary stroke.

### 8.9 Supply management

The IC starts up when the voltage at the VCC pin exceeds  $V_{startup}$ . The IC locks out (stops switching) when the voltage at the VCC pin drops to below  $V_{th(UVLO)}$ . The hysteresis between the start and stop levels allows the VCC capacitor to supply the IC during zero-crossings of the mains.

The SSL5261PT incorporates an internal VCC clamping circuit. The clamp limits the voltage on the VCC supply pin to the maximum value  $V_{clamp(VCC)}$ . If the maximum current of the external resistor minus the current consumption of the IC is lower than the limiting value of  $I_{VCC}$  in Table 4, no external Zener diode is required.

# 9. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                 | Parameter                        | Conditions               | Min   | Max   | Unit |

|------------------------|----------------------------------|--------------------------|-------|-------|------|

| Voltages               |                                  |                          |       | '     |      |

| V <sub>CC</sub>        | supply voltage                   | current limited [1][2    | 0.4   | +18   | V    |

| V <sub>I(SW)</sub>     | input voltage on pin SW          | current limited [1][2    | 0.4   | +22   | V    |

| V <sub>I(ISNS)</sub>   | input voltage on pin ISNS        |                          | -0.4  | +5    | V    |

| V <sub>I(FB)</sub>     | input voltage on pin FB          |                          | -0.4  | +5    | V    |

| $V_{IO(COMP)}$         | input/output voltage on pin COMP |                          | -0.4  | +5.3  | V    |

| V <sub>I(DEMOVP)</sub> | input voltage on pin<br>DEMOVP   |                          | -6    | +6    | V    |

| V <sub>I(DIM)</sub>    | input voltage on pin DIM         |                          | -0.4  | +5    | V    |

| Currents               |                                  |                          |       |       |      |

| I <sub>I(VCC)</sub>    | input current on pin VCC         |                          | -     | +8.8  | mA   |

| I <sub>I(SW)</sub>     | input current on pin SW          | RMS current              | -     | 380   | mA   |

|                        |                                  | duty cycle < 20 %        | -2    | +2    | Α    |

| I <sub>I(ISNS)</sub>   | input current on pin ISNS        | duty cycle < 20 %        | -2    | +2    | Α    |

| General                |                                  |                          |       |       |      |

| P <sub>tot</sub>       | total power dissipation          | T <sub>amb</sub> < 75 °C | -     | 0.28  | W    |

| T <sub>stg</sub>       | storage temperature              |                          | -55   | +150  | °C   |

| Tj                     | junction temperature             |                          | -40   | +160  | °C   |

| ESD                    |                                  |                          |       |       |      |

| V <sub>ESD</sub>       | electrostatic discharge          | class 1                  |       |       |      |

|                        | voltage                          | human body<br>model      | _2000 | +2000 | V    |

|                        |                                  | charged device [4] model | _500  | +500  | V    |

<sup>[1]</sup> The current into the VCC pin must not exceed the maximum  $I_{VCC}$  value.

<sup>[2]</sup> An internal clamp sets the supply voltage and current limits.

<sup>[3]</sup> Equivalent to discharge a 100 pF capacitor through a 1.5  $k\Omega$  series resistor.

<sup>[4]</sup> Charged device model: equivalent to charging the IC up to 1 kV and the subsequent discharging of each pin down to 0 V over a 1  $\Omega$  resistor.

### 10. Thermal characteristics

Table 5. Thermal characteristics

| Symbol                 | Parameter                                   | Conditions                                                                           | Тур | Unit |

|------------------------|---------------------------------------------|--------------------------------------------------------------------------------------|-----|------|

| R <sub>th(j-a)</sub>   | thermal resistance from junction to ambient | in free air; PCB;<br>2 cm × 3 cm; 2-layer;<br>35 μm copper/layer                     | 159 | K/W  |

|                        |                                             | in free air;<br>SO8 package; PCB;<br>JEDEC 2s2p                                      | 89  | K/W  |

| $\Psi_{	extsf{j-top}}$ | thermal resistance from junction to top     | top package<br>temperature<br>measured at the<br>warmest point on top<br>of the case | 4   | K/W  |

### 11. Characteristics

#### Table 6. Characteristics

$T_{amb}$  = 25 °C;  $V_{CC}$  = 15 V; all voltages are measured with respect to ground pin (pin 8); currents are positive when flowing into the IC; unless otherwise specified.

| Symbol                    | Parameter                                   | Conditions                                        | Min   | Тур  | Max   | Unit |

|---------------------------|---------------------------------------------|---------------------------------------------------|-------|------|-------|------|

| Supply (pin VC            | C)                                          | '                                                 |       |      |       |      |

| V <sub>startup</sub>      | start-up voltage                            |                                                   | 14.55 | 15   | 15.45 | V    |

| $V_{th(UVLO)}$            | undervoltage lockout threshold voltage      |                                                   | 9.7   | 10   | 10.3  | V    |

| V <sub>clamp(VCC)</sub>   | clamp voltage on pin VCC                    | I <sub>I(VCC)</sub> = 2.6 mA [1]                  | 15.4  | 16   | 16.6  | V    |

| V <sub>rst(latch)</sub>   | latched reset voltage                       |                                                   | 5.8   | 6.2  | 6.6   | V    |

| I <sub>CC(oper)</sub>     | operating supply current                    | switching at 100 kHz                              | 160   | 180  | 200   | μΑ   |

| I <sub>CC(dch)</sub>      | discharge supply current                    | $V_{CC} = V_{rst(latch)}$                         | 3.7   | -    | -     | mA   |

| Loop compens              | ation (pin COMP)                            |                                                   |       |      | '     |      |

| V <sub>IO(COMP)</sub>     | input/output voltage on pin COMP            | operating range in application                    | 2     | -    | 4     | V    |

| V <sub>ton(zero)</sub>    | zero on-time voltage                        |                                                   | 1.9   | 2.0  | 2.1   | V    |

| V <sub>ton(max)</sub>     | maximum on-time voltage                     |                                                   | 3.8   | 4.0  | 4.2   | V    |

| V <sub>clamp(COMP)</sub>  | clamp voltage on pin COMP                   | I <sub>I(COMP)</sub> = 1 mA                       | 4.4   | 4.8  | 5.2   | V    |

| t <sub>on(max)</sub>      | maximum on-time                             | V <sub>IO(COMP)</sub> = 4 V                       | 11.5  | 14.5 | 17.5  | μS   |

| I <sub>O(COMP)</sub>      | output current on pin COMP                  | V <sub>I(ISNS)</sub> = 0 V                        | -3.6  | -3.0 | -2.4  | μΑ   |

| Valley detection          | n and overvoltage detection (pin E          | DEMOVP)                                           |       |      |       | '    |

| I <sub>prot(DEMOVP)</sub> | protection current on pin DEMOVP            | open pin current;<br>V <sub>I(DEMOVP)</sub> = 0 V | -250  | -180 | -50   | nA   |

| $V_{th(ovp)}$             | overvoltage protection threshold voltage    |                                                   | 1.75  | 1.82 | 1.89  | V    |

| N <sub>cy(ovp)</sub>      | number of overvoltage protection cycles     |                                                   | -     | 3    | -     | -    |

| (dV/dt) <sub>vrec</sub>   | valley recognition voltage change with time | [2]                                               | -     | -3.8 | -     | V/μs |

Silergy Corp.

# SSL5261PT

#### Mains dimmable LED driver IC

Table 6. Characteristics ...continued

$T_{amb}$  = 25 °C;  $V_{CC}$  = 15 V; all voltages are measured with respect to ground pin (pin 8); currents are positive when flowing into the IC; unless otherwise specified.

| Symbol                       | Parameter                                    | Conditions                                 | Min   | Тур   | Max   | Unit |

|------------------------------|----------------------------------------------|--------------------------------------------|-------|-------|-------|------|

| V <sub>det(demag)</sub>      | demagnetization detection voltage            |                                            | 6     | 20    | 34    | mV   |

| t <sub>sup(xfmr_ring)</sub>  | transformer ringing suppression time         |                                            | 1.13  | 1.45  | 1.77  | μS   |

| Current sensing (            | oin ISNS)                                    |                                            |       |       |       |      |

| V <sub>I(ISNS)</sub>         | input voltage on pin ISNS                    | operating range in application             | 0     | -     | 0.9   | V    |

| $V_{I(min)ISNS}$             | minimum input voltage on pin ISNS            |                                            | 15    | 25    | 35    | mV   |

| V <sub>I(max)ISNS</sub>      | maximum input voltage on pin ISNS            |                                            | 8.0   | 0.9   | 1.0   | V    |

| t <sub>on(min)</sub>         | minimum on-time                              | [3]                                        | 280   | 380   | 480   | ns   |

| t <sub>d</sub>               | delay time                                   | [3]                                        | -     | 100   | -     | ns   |

| Regulation contro            | l (pin FB)                                   |                                            |       |       |       |      |

| $V_{I(FB)}$                  | input voltage on pin FB                      | operating range in application             | 0     | -     | 1.8   | V    |

| g <sub>m(FB)</sub>           | FB transconductance                          | V <sub>I(FB)</sub> to I <sub>O(COMP)</sub> | 18    | 19.3  | 20.6  | μA/V |

| V <sub>intregd(max)</sub> FB | maximum internal regulated voltage on pin FB | V <sub>I(DIM)</sub> > 0.9 V                | 0.150 | 0.155 | 0.160 | V    |

| V <sub>clamp(FB)</sub>       | clamp voltage on pin FB                      | I <sub>I(FB)</sub> = 1 mA                  | 4.2   | 4.4   | 4.6   | V    |

| Dimming control (            | pin DIM)                                     |                                            |       |       |       |      |

| $V_{I(DIM)}$                 | input voltage on pin DIM                     | operating range in application             | 0     | -     | 0.9   | V    |

| $G_{dim}$                    | dimming gain                                 | $\frac{V_{I(ISNS)}}{V_{I(DIM)}}$           | 0.9   | 1     | 1.1   | V/V  |

| V <sub>clamp(DIM)</sub>      | clamp voltage on pin DIM                     | I <sub>I(DIM)</sub> = 200 μA               | 4.3   | 4.5   | 4.7   | V    |

| Driver (pin SW)              |                                              |                                            |       |       |       |      |

| R <sub>DSon</sub>            | on-state resistance                          | T <sub>j</sub> = 25 °C                     | -     | 0.87  | 0.94  | Ω    |

|                              |                                              | T <sub>j</sub> = 125 °C                    | -     | 1.2   | -     | Ω    |

| t <sub>off(max)</sub>        | maximum off-time                             |                                            | 30    | 40    | 50    | μS   |

| Temperature prote            | ection                                       |                                            |       |       |       |      |

| T <sub>pl(IC)</sub>          | IC protection level temperature              |                                            | 140   | 150   | 165   | °C   |

| T <sub>pl(IC)rst</sub>       | reset IC protection level temperature        |                                            | 106   | 118   | 130   | °C   |

- [1] The start-up voltage and the clamp voltage are correlated.

- [2] Guaranteed by design.

- [3]  $t_{leb} = t_{on(min)} t_d$ ;  $t_{on(min)}$  is only effective when OCP is triggered.

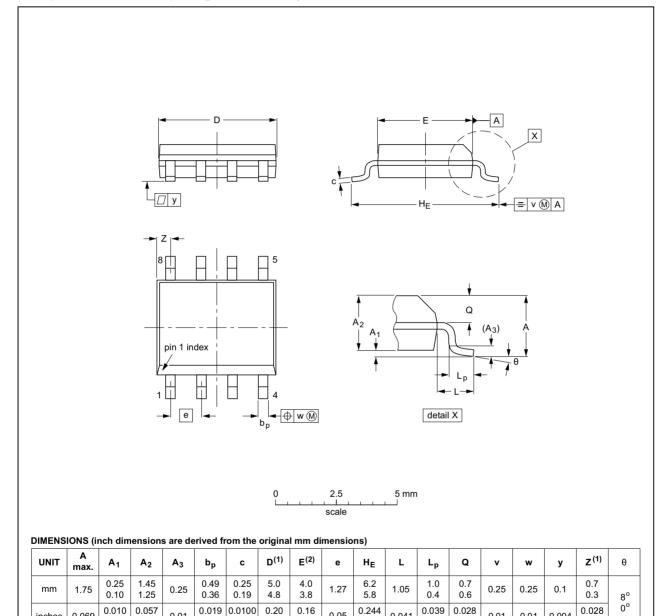

## 12. Package outline

#### SO8: plastic small outline package; 8 leads; body width 3.9 mm

SOT96-1

inches

0.069

1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

0.014 | 0.0075

2. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

0.01

0.049

| OUTLINE |        | REFER  | ENCES | EUROPEAN   | ISSUE DATE                      |

|---------|--------|--------|-------|------------|---------------------------------|

| VERSION | IEC    | JEDEC  | JEITA | PROJECTION | ISSUE DATE                      |

| SOT96-1 | 076E03 | MS-012 |       |            | <del>99-12-27</del><br>03-02-18 |

0.05

0.041

0.01

0.01

0.004

Package outline SOT96-1 (SO8) Fig 7.