## 1. General description

The SSL5301T is a mains dimmable controller IC, intended to drive dimmable LEDs in general lighting applications.

The main benefits of this IC include:

- · High dimmer compatibility

- Selectable modes for high power factor or low ripple, allowing a wide LED power range

- Large dimming range

- · Single stage topology for small PCB footprint

- · Ease of design-in

- Integrated start-up JFET

- Low electronic Bill Of Material (BOM)

- · Supports multi-lamp applications

- · Various converter topologies supported

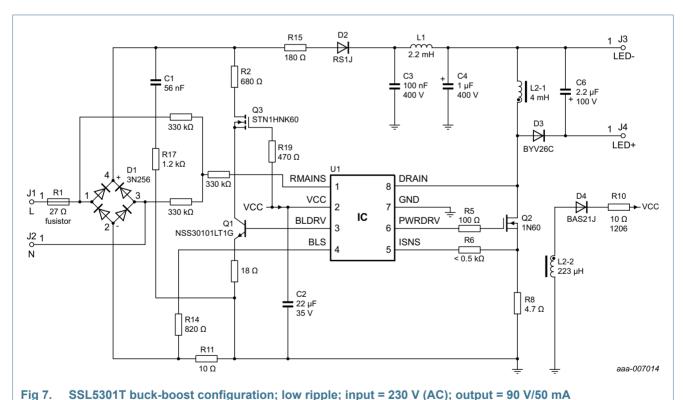

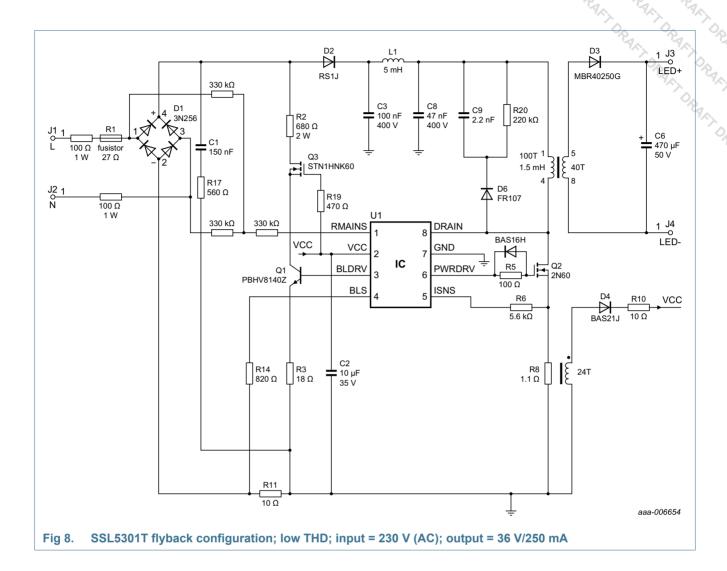

The IC drives an external switch for easy power scaling. It has been designed to start up directly from the High-Voltage (HV) supply by an internal high-voltage current source. Flyback, buck and buck-boost circuit topologies are supported. Primary side sensing provides accurate output current control.

The IC can detect all known mains dimmer types and translate the dimmer setting to a continuous LED current in multiple ways. It can operate in three switching modes at two switching frequency ranges. It offers tradeoffs between the output current ripple, the mains current Total Harmonic Distortion (THD) and the application size. The IC incorporates all required protection features.

#### 2. Features and benefits

- LED controller IC for driving strings of LEDs or high-voltage LEDs from rectified mains

- High-efficiency switch mode buck, flyback or buck-boost controller driving an external power FET

- Two maximum switching frequencies for highest efficiency or smallest application size

- ◆ Zero current switching at switch turn-on

- Zero voltage or valley switching at switch turn-on

- Selectable low THD or low LED current ripple modes

Silergy Corp. SS

#### Mains dimmable controller for LED lighting

- Leading, trailing and intelligent dimmer detection

- Two built-in dim curves

- LED current accuracy within ±4 % across variations in components and conditions

- No binning on LED forward voltage required

- Built-in Protections:

- UnderVoltage LockOut (UVLO)

- ◆ Leading Edge Blanking (LEB)

- OverCurrent Protection (OCP)

- Internal OverTemperature Protection (OTP)

- Brownout protection

- Output Short Protection (OSP)

- Output open OverVoltage Protection (OVP)

- Mains synchronization loss protection

- Bleeder dissipation protection

- Low component count LED driver solution

- Compatible with wall switches with built-in indication light during standby

- Operates well in multiple-lamp arrangements

- IC lifetime matches or surpasses LED lamp lifetime

## 3. Applications

Compact mains dimmable LED lamps with accurate, dimmable current output for single mains voltages, including 100 V (AC), 120 V (AC) and 230 V (AC). External components determine the power level. The power level ranges from 4 W to over 25 W. Applications fit in common form factors like PAR, GU10, A19, and the candle form factor.

## 4. Quick reference data

#### Table 1. Quick reference data

$T_{amb}$  = 25 °C;  $V_{CC}$  = 19.5 V; all voltages are measured with respect to the ground pin; currents are positive when flowing into the IC; unless otherwise specified.

| Symbol          | Parameter           | Conditions                       | Min | Тур | Max | Unit |

|-----------------|---------------------|----------------------------------|-----|-----|-----|------|

| V <sub>CC</sub> | supply voltage      |                                  | 8.8 | -   | 32  | V    |

| f <sub>sw</sub> | switching frequency | low-frequency mode; undimmed     |     |     |     |      |

|                 |                     | 50 Hz mains                      | 55  | 60  | 65  | kHz  |

|                 |                     | 60 Hz mains                      | 66  | 72  | 78  | kHz  |

|                 |                     | high-frequency mode;<br>undimmed |     |     |     |      |

|                 |                     | 50 Hz mains                      | 84  | 91  | 98  | kHz  |

|                 |                     | 60 Hz mains                      | 101 | 109 | 117 | kHz  |

| Silergy Co                                                       | rp.                                                                                             |                                      | <b>~</b>            | 7           | <del>. 7</del> 7. | 5301T          | 70.        |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------|---------------------|-------------|-------------------|----------------|------------|

| Table 4 C                                                        |                                                                                                 |                                      | Mains dimmak        | oie contro  | piler for L       |                | 5          |

| T <sub>amb</sub> = 25 °C; ∨                                      | ick reference datacontinu<br>/ <sub>CC</sub> = 19.5 V; all voltages are<br>otherwise specified. | ued<br>e measured with respect to th | ne ground pin; curr | ents are po | sitive whei       | n flowing into | Op PAN     |

| T <sub>amb</sub> = 25 °C; ∨                                      | $V_{CC}$ = 19.5 V; all voltages are                                                             |                                      | ne ground pin; curr | ents are po | Max               | n flowing into | PAR        |

| T <sub>amb</sub> = 25 °C; V<br>the IC; unless o                  | V <sub>CC</sub> = 19.5 V; all voltages are otherwise specified.                                 | e measured with respect to th        |                     |             |                   | Op             | PAK ORAKIO |

| T <sub>amb</sub> = 25 °C; V<br>the IC; unless o<br><b>Symbol</b> | V <sub>CC</sub> = 19.5 V; all voltages are otherwise specified.  Parameter                      | e measured with respect to th        |                     | Тур         |                   | Unit           | RAK DRAKE  |

## **Ordering information**

#### Table 2. **Ordering information**

| Type number | Package | ackage                                                         |         |  |  |  |  |

|-------------|---------|----------------------------------------------------------------|---------|--|--|--|--|

|             | Name    | Description                                                    | Version |  |  |  |  |

| SSL5301T    | SO8     | plastic small package outline body; 8 leads; body width 3.9 mm | SOT96-1 |  |  |  |  |

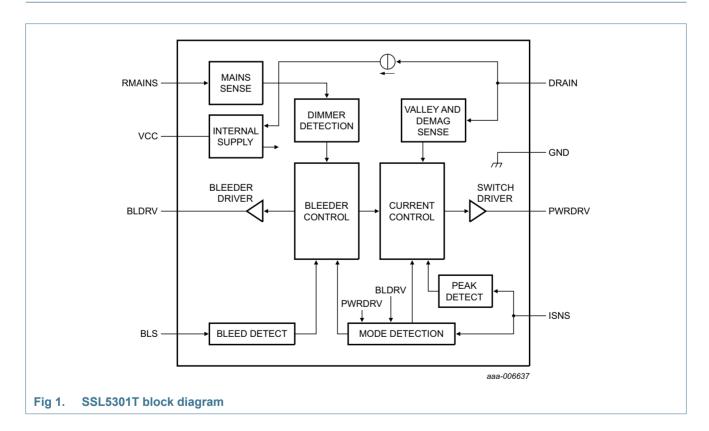

## **Block diagram**

SSL5301T

Mains dimmable controller for LED lighting

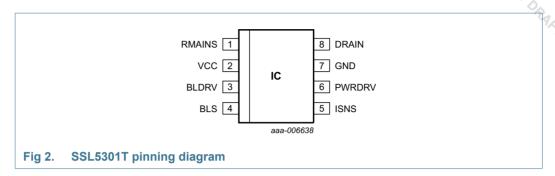

## 7. Pinning information

## 7.1 Pinning

### 7.2 Pin description

Table 3. Pin description

| Symbol | Pin | Description                           |

|--------|-----|---------------------------------------|

| RMAINS | 1   | mains detection input                 |

| VCC    | 2   | IC supply input/output                |

| BLDRV  | 3   | bleeder stage transistor drive output |

| BLS    | 4   | bleeder loop sense                    |

| ISNS   | 5   | peak current sense input              |

| PWRDRV | 6   | external MOSFET gate driver output    |

| GND    | 7   | ground                                |

| DRAIN  | 8   | external MOSFET drain sense input     |

# 8. Functional description

#### 8.1 Pin functionality

#### 8.1.1 Pin RMAINS

The RMAINS pin takes in a current representing the rectified mains or dimmer output voltage via the external RMAINS resistors. The low ohmic input results in current always flowing, causing the voltage on the RMAINS pin to remain below the maximum  $V_{i(RMAINS)}$  at any time.

The information about the mains voltage is used to set the dimming level and to shape the output current waveform in LTHD modes. It is also used for internal timing synchronizations, making it essential for low-ripple applications.

Some filtering may be required outside of the IC to eliminate incoming noise.

If the pin does not receive a rectified mains signal, the mains synchronization loss protection is triggered.

Silergy Corp. SSL

#### Mains dimmable controller for LED lighting

#### 8.1.2 Pin VCC

At power-up, the VCC pin and its capacitor are charged using the internal HV current source from the DRAIN pin. Once  $V_{CC}$  has reached  $V_{CC(startup)}$ , switching starts and  $V_{CC}$  supply is generated from the auxiliary winding. If  $V_{CC}$  exceeds  $V_{ovp(VCC)}$  due to, for example, a disconnected output, OVP is triggered. If  $V_{CC}$  drops to  $V_{CC(low)}$ , the internal HV current source is enabled. If  $V_{CC}$  drops below  $V_{CC(stop)}$ , UVLO protection is triggered.

Do not use the VCC pin to power additional circuitry outside the IC because no additional current budget is guaranteed. An additional  $V_{CC}$  load can affect product performance.

To support wall switches that include an indicator light, a predetermined current ( $I_{CC}$ ) is pulled from the supply during a limited window of the VCC voltage (see condition 2 of  $I_{CC}$  in Table 7).

#### 8.1.3 Pin BLDRV

The BLDRV pin drives an external high-voltage NPN transistor stage. This stage is used to generate additional load current for a dimmer (see <u>Section 8.2.6</u>). Or it is used to load the mains during zero crossings when no dimmer is connected. It ensures proper mains detection. The voltage range is adapted to bipolar transistors only. At low BLDRV output voltage, the drive capability is reduced to limit current loss in case of bipolar transistor saturation.

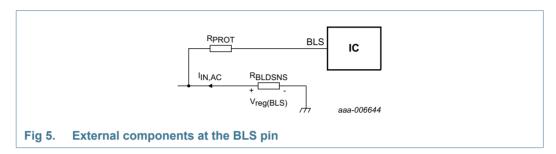

#### 8.1.4 Pin BLS

The BLS pin senses the total application current for dimmer compatibility (bleed sense, see Section 8.2.6).

**Remark:** A series resistor must be present between the BLS pin and the bleed loop sense resistor. The series resistor prevents that the current flowing out of the pin exceeds the limiting value,  $I_{i(BLS)}$ .

#### 8.1.5 **Pin ISNS**

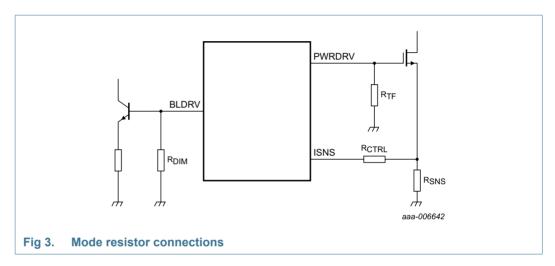

The ISNS pin senses the voltage across the sense resistor, R<sub>SNS</sub>, generated by the inductor current flowing through the external MOSFET and this resistor (see Figure 3).

Optionally, a mode definition resistor is present between the pin and the current sense resistor. At start-up, the mode resistor is measured using a current which is sourced out of the pin.

#### 8.1.6 Pin PWRDRV

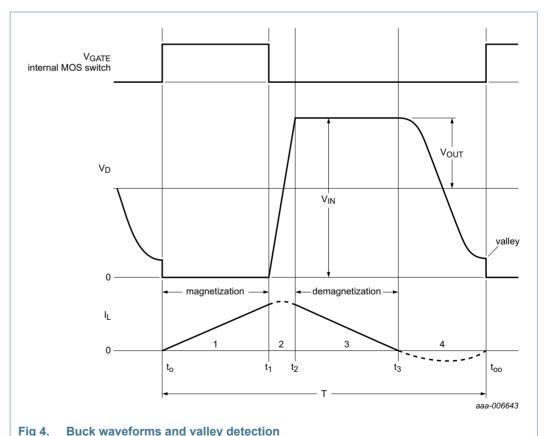

The SSL5301T is equipped with a driver that controls an external MOSFET. The voltage on the driver output pin is increased towards the maximum  $V_{o(PWRDRV)}$  to open the switch during the first cycle (t0 to t1; see <u>Figure 4</u>). It is pulled to ground from the start of the secondary stroke until the next cycle starts (t1 to t00).

#### 8.1.7 Pin DRAIN

The DRAIN pin is used to derive energy to charge the VCC pin at start-up and after switching is stopped because of a triggered protection. The signal at the DRAIN pin is used to detect the occurrence of demagnetization. It is also used to determine the valley of the ringing voltage for starting the primary stroke.

## 8.2 Converter operation

#### 8.2.1 Available modes

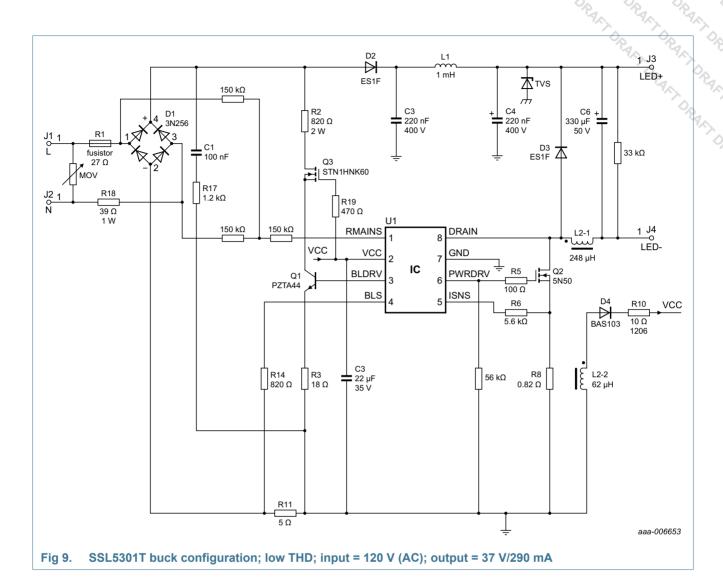

The SSL5301T incorporates various built-in operation modes which can be selected in the application using a maximum of three external resistors. At start-up, the value of these resistors is detected and the corresponding operation mode is set.

Mode resistors  $R_{TF}$  and  $R_{DIM}$  at the PWRDRV and BLDRV pins are connected between the pin and ground. Mode resistor  $R_{CTRL}$  at the ISNS pin is connected between the pin and the external MOSFET source (see Figure 3).

Table 4 gives an overview of the available modes.

Table 4. Available modes

| Parameter              | How to set                    | Options                           | Mode resistor value      |

|------------------------|-------------------------------|-----------------------------------|--------------------------|

| topology and frequency | R <sub>TF</sub> on pin PWRDRV | flyback or buck-boost;<br>HF mode | $\infty$                 |

|                        |                               | buck; HF mode                     | 56 kΩ                    |

|                        |                               | buck; LF mode                     | 33 kΩ                    |

|                        |                               | flyback or buck-boost;<br>LF mode | 15 kΩ                    |

| dim curve              | R <sub>DIM</sub> on pin BLDRV | curve 1; lin-log                  | 10 kΩ                    |

|                        |                               | curve 2; lin-log limited          | $\infty$                 |

| control mode           | R <sub>CTL</sub> on pin ISNS  | low ripple (PF < 0.7)             | 0 kΩ to 0.5 kΩ or 3.3 kΩ |

|                        |                               | eco-LTHD (PF ~ 0.75)              | 1.5 kΩ                   |

|                        |                               | LTHD (PF > 0.9)                   | 5.6 kΩ                   |

#### 8.2.2 Switching scheme

The converter in the SSL5301T is a Discontinuous Conduction Mode (DCM), peak current controlled system. When the output current control system requires a new switching cycle and the inductor current is zero, the external MOSFET is turned on at the next detected valley (see <u>Section 8.2.3</u>). The inductor current increases until a maximum, defined by the regulation loop, is reached and the external MOSFET is switched off. The inductor current

Silergy Corp. SSL5301T

#### Mains dimmable controller for LED lighting

reduces again. When the inductor current reaches zero, it is detected at the DRAIN pin. The detection enables the control system to regulate to an accurate average value of the LED current.

The maximum switching frequency can be set at two rates (see Section 8.2.1).

Three options are available which determine how the controller adjusts the maximum inductor peak current over the mains cycle. The result is either an optimal input current shape (optimized power factor and THD), a minimal LED current ripple, or an intermediate solution (eco-LTHD mode).

#### 8.2.3 Valley detection

A new cycle is started when the primary switch is switched on (see Figure 4). At a certain time (t1), the switch is switched off and the secondary stroke starts. After the secondary stroke (t3) has ended, the drain voltage shows oscillation or ringing. Circuitry at the DRAIN pin senses when the voltage on the drain of the switch has reached its lowest value (valley) during each oscillation. When the control loop requires the next cycle, it is started the next time a valley occurs. As a result, the capacitive switching losses reduce significantly. For successful valley detection, the frequency and amplitude of the drain voltage ringing must cause the slope of the ringing voltage to exceed the detection limit  $(\Delta V/\Delta t)_{\text{vrec}}$  for at least  $t_{\text{d(vrec-swon)}}$ .

#### Mains dimmable controller for LED lighting

#### 8.2.4 Output current settings

The IC regulates the output LED current with great accuracy over line, load and component variations. The user can set the full-scale (100 %) value of the LED current. Choose a current sense resistor value, using Equation 1:

$$I_{LED} = \frac{V_{reg}}{R_{SNS}} \times N \tag{1}$$

#### Where:

- V<sub>reg</sub> is the set point of the internal regulation loop: 117 mV for LTHD buck-boost/flyback and 234 mV for LTHD buck and low ripple buck-boost/flyback, and 469 mV for low-ripple buck.

- R<sub>SNS</sub> is the sense resistor on pin ISNS (see Figure 3)

- N is the transformer ratio.

The IC regulates the output current. It controls the current sense threshold voltage  $V_{th(ISNS)}$ , the number of switching cycles per (half-)mains period, and, if necessary, the switching frequency. The regulation depends on the mode of operation.

#### 8.2.5 Preventing Continuous Conduction Mode (CCM)

To enable application design without having to include margins to ensure DCM operation, a CCM-prevention feature has been built in. The IC monitors the time gap between the end of the secondary stroke and the start of the next cycle. If this time becomes smaller than a predetermined idle time of about 1.8  $\mu s$ , the controller reduces the switching frequency.

#### 8.2.6 Dimming support

The SSL5301T can detect both leading edge and trailing-edge mains dimmer presence, as well as no dimmer presence at all. Support for smart dimmers that take additional supply current pulses is included. The phase information from the dimmer is translated to an LED output current level. To enable the application design for either optimal dimmer compatibility or limited bleeder power consumption, the following features are included:

#### • Bleeder stage support:

The BLDRV pin is tailored to drive an external low-cost high-voltage NPN transistor, which creates a bleed current controlled by the SSL5301 internal control circuitry. The resulting bleed current is modulated over the mains phase to ensure correct dimmer operation

- A strong bleed current is generated around the expected cutting edge of the dimmer output voltage. This edge is detected at the RMAINS pin. The NPN emitter resistor determines the maximum bleed current, given the maximum V<sub>o(BLDRV)</sub>. An additional collector resistor can be added to distribute the bleeder stage power dissipation over its components. Reducing the current sourced at this pin according to its voltage level (I<sub>source(high)BLDRV</sub>) limits current dissipation via the BLDRV pin.

- A weak bleed current is generated to keep the dimmer in conduction when triggered. The generation of the weak bleed current is achieved when the total current to the dimmer is fed through a sense resistor R<sub>BLDSNS</sub> (see Figure 5). The

Silergy Corp. SSL53

#### Mains dimmable controller for LED lighting

resulting voltage is measured at the BLS pin. A control loop in the IC uses this voltage to drive the external bleeder stage. The resulting bleeder current adds to the converter current so that the total current drawn by the application is kept constant.

The regulation target voltage over R<sub>BLDSNS</sub> equals V<sub>th(reg)BLS</sub>.

The reason for the additional resistor R<sub>PROT</sub> is described in Section 8.1.4.

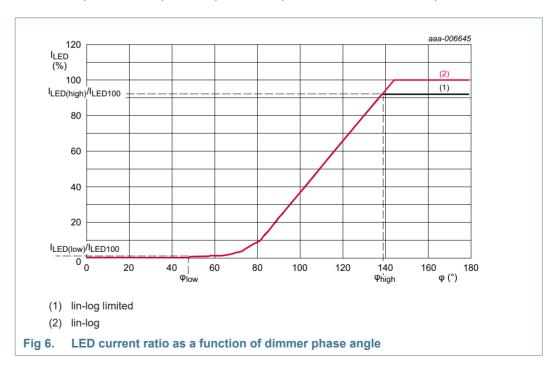

#### · Dimming curves:

Two dimming curves are available to translate the detected dimmer phase to an output current level.  $I_{LED(low)}/I_{LED100}$  gives the minimum output current level as a ratio of the full-scale current for either curve. The mode resistor at the BLDRV pin determines the selection (see Figure 6).

- The lin-log curve has a smooth tail that matches human eye light sensitivity.

- The lin-log limited curve enables optimal thermal lamp design. When no dimmer is detected, the output current is set to 100 %. When a dimmer is detected, the lin-log limited curve is used. The result is a lower maximum output current at a total power dissipation that equals the power dissipated when no dimmer is present.

#### Mains dimmable controller for LED lighting

#### 8.3 Protections

The IC incorporates the following protections:

- UnderVoltage LockOut (UVLO

- OverCurrent Protection (OCP)

- Brownout Protection

- Output Short Protection (OSP)

- Output open OverVoltage Protection (OVP)

- Internal OverTemperature Protection (OTP)

- · Mains synchronization loss protection

- Leading Edge Blanking (LEB)

- · Bleeder dissipation protection

Output open OVP is a latched protection. Power-off cycling is required to exit the latched state. All other protections are not latched and lead to a safe restart of the converter.

#### 8.3.1 UnderVoltage LockOut (UVLO)

When the voltage on the VCC pin drops below the value of  $V_{CC(stop)}$ , the IC stops switching. The internal HV current source is enabled. Once  $V_{CC}$  has increased to  $V_{CC(startup)}$  the IC restarts after a minimum of 1 s back-off time.

#### 8.3.2 OverCurrent Protection (OCP)

The SSL5301T contains a highly accurate peak current detector. It triggers when the voltage at pin ISNS reaches  $V_{th(ISNS)}$ . The circuit is activated after the leading edge blanking time ( $t_{leb}$ ). There is a propagation delay between the peak current detection and the switch actually switching off. Due to this delay, the actual peak current is slightly higher than the peak current level set by the current sense resistor. The control loop compensates for this difference ensuring output current accuracy.

#### 8.3.3 Brownout protection

The brownout protection is designed to limit the switch-on time in case of low input voltage. Because of the built-in peak current control, the input current otherwise slowly increases while no power is transferred to the output in a flyback configuration. The SSL5301T includes a maximum on-time of the switch  $t_{on(high)}$ .

#### 8.3.4 Output short protection (OSP)

If, during the secondary stroke (switch-off time), a valley is not detected within the off-time limit ( $t_{off(high)}$ ), the output voltage is typically less than the minimum limit allowed in the application. This condition can occur either during starting up or due to a short. A timer is started when  $t_{off(high)}$  is detected, and is stopped only if a valid valley-detection occurs in one of the subsequent cycles. If no valley is detected for  $t_{det(sc)}$ , it is concluded that a real short-circuit exists and not a temporary start-up situation. The IC enters standby mode and tries to restart after a minimum of 9 s back-off time.

Silergy Corp. SSL

#### Mains dimmable controller for LED lighting

#### 8.3.5 Output open OverVoltage Protection (OVP)

The result of an output open situation is that no power is delivered to the output, causing  $V_{CC}$  to increase and exceed  $V_{CC(max)}$ . Upon detection of this event, the IC enters the standby mode. The IC does not restart as long as mains voltage is present.

#### 8.3.6 Internal OverTemperature Protection (OTP)

When the internal OTP function is triggered, the converter stops operating. This function is triggered at  $T_{th(act)otp}$ . The Overtemperature protection is an auto-restart protection. The IC restarts when the IC temperature drops below  $T_{th(rel)otp}$ .

#### 8.3.7 Mains synchronization loss protection

When the input current at the RMAINS pin fails to cross the "zero crossing detection" value of  $I_{i(RMAINS)}$ , no mains cycles are detected. If this situation persists for a time  $t_{d(mld)}$ , the IC stops switching. Once a valid mains signal is available again, the IC restarts.

#### 8.3.8 Leading Edge Blanking (LEB)

A blanking time is implemented after switch-on to prevent premature detection of inductor peak current. At the opening of the MOSFET switch, a short current spike can occur because of the capacitive discharge of voltage over the drain and source. During the leading edge blanking time ( $t_{leb}$ ), detection is disabled, so spikes are disregarded.

#### 8.3.9 Bleeder dissipation protection

To limit dissipation in the bleeder, the dimmer detection state is limited to 16 mains half-cycles. If dimmer detection is not successfully completed, the IC restarts after a minimum of 9 s back-off time.

## 9. Limiting values

Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                 | Parameter                   | Conditions                            | Min  | Max  | Unit |

|------------------------|-----------------------------|---------------------------------------|------|------|------|

| General                |                             |                                       |      |      | '    |

| P <sub>tot</sub>       | total power dissipation     | SO8 package                           | -    | 0.6  | W    |

| T <sub>amb</sub>       | ambient temperature         |                                       | -40  | +125 | °C   |

| Tj                     | junction temperature        |                                       | -40  | +190 | °C   |

| T <sub>stg</sub>       | storage temperature         |                                       | -55  | +150 | °C   |

| SR                     | slew rate                   | pin DRAIN                             | -10  | +10  | V/ns |

| Pin voltage            | es and currents             |                                       |      |      | '    |

| V <sub>CC</sub>        | supply voltage              |                                       | -0.4 | +34  | V    |

| V <sub>i(RMAINS)</sub> | input voltage on pin RMAINS | current limited                       | -0.4 | +5.2 | V    |

| I <sub>i(RMAINS)</sub> | input current on pin RMAINS | at V <sub>(RMAINS)</sub> = 5.2 V      | 0    | 1    | mA   |

| V <sub>i(BLS)</sub>    | input voltage on pin BLS    | current limited                       | -0.7 | +5.2 | V    |

| I <sub>i(BLS)</sub>    | input current on pin BLS    |                                       | -2.5 | +2.5 | mA   |

| V <sub>i(ISNS)</sub>   | input voltage on pin ISNS   |                                       | -0.4 | +5.2 | V    |

| $V_{i(DRAIN)}$         | input voltage on pin DRAIN  | during mains surge;<br>not repetitive | -0.4 | +700 | V    |

## Mains dimmable controller for LED lighting

Table 5. Limiting values ...continued

|                  |                                                          | Mains dimmable co            |       | L53   |           |

|------------------|----------------------------------------------------------|------------------------------|-------|-------|-----------|

|                  | Limiting valuescontinued<br>be with the Absolute Maximun | n Rating System (IEC 60134). |       | OPAA. | OPAN OPAN |

| Symbol           | Parameter                                                | Conditions                   | Min   | Max   | Unit      |

| V <sub>ESD</sub> | electrostatic discharge                                  | human body model [1]         |       |       | 7/2       |

|                  | voltage                                                  | all pins except pin<br>DRAIN | -2000 | +2000 | V         |

|                  |                                                          | pin DRAIN                    | -1000 | +1000 | V         |

|                  |                                                          | charged device [2] model     | -500  | +500  | V         |

- [1] Human body model: equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor.

- [2] Charged device model: equivalent to charging the IC up to 1 kV and the subsequent discharging of each pin down to 0 V over a 1  $\Omega$  resistor.

### 10. Thermal characteristics

Table 6. Thermal characteristics

| Symbol                 | Parameter                                                          | Conditions                                                                  | Тур  | Unit |

|------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------|------|------|

| R <sub>th(j-a)</sub>   | thermal resistance from junction to ambient                        | in free air; PCB:<br>2 cm × 3 cm;<br>2-layer; 35 μm Cu/layer                | 159  | K/W  |

|                        |                                                                    | in free air;<br>PCB: JEDEC 2s2p                                             | 89   | K/W  |

| $\Psi_{	extsf{j-top}}$ | thermal characterization parameter from junction to top of package | top package temperature<br>measured at the warmest<br>top of the case point | 0.49 | K/W  |

### 11. Characteristics

#### Table 7. **Characteristics**

T<sub>amb</sub> = 25 °C; V<sub>CC</sub> = 19.5 V; all voltages are measured with respect to the ground pin; currents are positive when flowing into the IC; unless otherwise specified.

| Symbol                   | Parameter                                 | Conditions                                                            | Min      | Тур  | Max  | Unit |

|--------------------------|-------------------------------------------|-----------------------------------------------------------------------|----------|------|------|------|

| High voltage             |                                           |                                                                       |          |      |      |      |

| V <sub>I(DRAIN)</sub>    | input voltage on pin DRAIN                | [1                                                                    | <u> </u> | -    | 675  | V    |

| I <sub>i(DRAIN)</sub>    | input current on pin DRAIN                | JFET on strong;<br>V <sub>DRAIN</sub> = 675 V; V <sub>CC</sub> = 17 V | 4.4      | 6.4  | 8.4  | mA   |

|                          |                                           | JFET on weak;<br>V <sub>DRAIN</sub> = 675 V; V <sub>CC</sub> < 4 V    | 500      | 550  | 600  | μА   |

|                          |                                           | JFET off; V <sub>DRAIN</sub> = 675 V;<br>V <sub>CC</sub> = 20 V       | -        | -    | 15   | μА   |

| Supply                   |                                           |                                                                       |          |      |      |      |

| V <sub>CC(startup)</sub> | start-up supply voltage                   |                                                                       | 17.5     | 18.5 | 19.5 | V    |

| V <sub>CC(low)</sub>     | low supply voltage                        | pin VCC                                                               | 11.2     | 11.8 | 12.4 | V    |

| V <sub>CC(stop)</sub>    | stop supply voltage                       |                                                                       | 8.8      | 9.3  | 9.8  | V    |

| V <sub>CC(hys)</sub>     | hysteresis of supply voltage              | between V <sub>startup</sub> and V <sub>stop</sub>                    | 8.5      | 9.1  | 9.7  | V    |

| V <sub>ovp(VCC)</sub>    | overvoltage protection voltage on pin VCC |                                                                       | 28       | 30   | 32   | V    |

|                                            |                                                            | Mains dir                                                                     | nmable co     | SS<br>introller fo | r LED     | lightin   |

|--------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------|---------------|--------------------|-----------|-----------|

|                                            |                                                            |                                                                               |               | PAX                | > PA      | 3         |

|                                            |                                                            | sured with respect to the ground pir                                          | n; currents a | re positive v      | vhen flov | ving into |

| Symbol                                     | Parameter                                                  | Conditions                                                                    | Min           | Тур                | Max       | Unit      |

| Icc                                        | supply current                                             | pin DRAIN; V <sub>CC</sub> < 4 V;<br>standby mode                             | -             | 0.1                | 0.2       | mA        |

|                                            |                                                            | pin DRAIN;<br>4 V < V <sub>CC</sub> < V <sub>CC(low)</sub> ;<br>standby mode  | 1             | 1.25               | 1.5       | mA        |

|                                            |                                                            | pin DRAIN; V <sub>CC</sub> > V <sub>CC(low)</sub> ;<br>standby mode           | -             | 0.2                | -         | mA        |

|                                            |                                                            | pin VCC; normal operation,<br>excluding drive currents to<br>BLDRV and PWRDRV | -             | 2.25               | -         | mA        |

| Current regulato                           | r and protection                                           |                                                                               |               |                    | '         |           |

| f <sub>sw</sub>                            | switching frequency                                        | low-frequency mode;<br>undimmed                                               |               |                    |           |           |

|                                            |                                                            | 50 Hz mains                                                                   | 55            | 60                 | 65        | kHz       |

|                                            |                                                            | 60 Hz mains                                                                   | 66            | 72                 | 78        | kHz       |

|                                            |                                                            | high-frequency mode;<br>undimmed                                              |               |                    |           |           |

|                                            |                                                            | 50 Hz mains                                                                   | 84            | 91                 | 98        | kHz       |

|                                            |                                                            | 60 Hz mains                                                                   | 101           | 109                | 117       | kHz       |

| I <sub>LED(low)</sub> /I <sub>LED100</sub> | low LED current ratio                                      | [2]                                                                           | -             | 0.008              | -         | -         |

| $I_{\rm LED(high)}/I_{\rm LED100}$         | high LED current ratio                                     | lin-log limited curve; dimmer [2] present                                     | -             | 0.92               | -         | -         |

| Φlow                                       | low phase                                                  |                                                                               | -             | 48                 | -         | 0         |

| Φhigh                                      | high phase                                                 | lin-log curve                                                                 | -             | 144                | -         | 0         |

|                                            |                                                            | lin-log limited curve                                                         | -             | 137                | -         | 0         |

| V <sub>th(high)ISNS</sub>                  | high threshold voltage on pin ISNS                         | at peak current                                                               | 1.195         | 1.24               | 1.285     | V         |

| $V_{th(low)ISNS}$                          | low threshold voltage on pin ISNS                          | (eco-)LTHD mode; at peak current                                              | 0.75          | 0.78               | 0.81      | V         |

|                                            |                                                            | low-ripple mode                                                               | 0.33          | 0.35               | 0.37      | V         |

| t <sub>leb</sub>                           | leading edge blanking time                                 |                                                                               | -             | 600                | -         | ns        |

| Valley detection                           |                                                            |                                                                               |               |                    |           |           |

| $(\Delta V/\Delta t)_{Vrec}$               | valley recognition voltage change with time negative slope | voltage ringing on pin<br>DRAIN                                               | -26           | -16                | -6        | V/μs      |

| t <sub>d(vrec-swon)</sub>                  | valley recognition to switch-on delay time                 |                                                                               | -             | 100                | -         | ns        |

| $T_{amb} = 25 ^{\circ}\text{C}; \ V_{CC} = 15$<br>the IC; unless otherwise<br>Symbol Position | se specified.<br>arameter                                      | Conditions  low-frequency mode 50 Hz mains 60 Hz mains | Min  13.2 | re positive v | when flow | wing into |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------|-----------|---------------|-----------|-----------|

| the IC; unless otherwis  Symbol Pa  Brownout protection                                       | se specified.<br>arameter                                      | low-frequency mode 50 Hz mains 60 Hz mains             | Min       |               |           | 00        |

| Brownout protection                                                                           | 1                                                              | low-frequency mode 50 Hz mains 60 Hz mains             |           | Тур           | IVIAX     | Onit      |

|                                                                                               |                                                                | 50 Hz mains<br>60 Hz mains                             | 13.2      |               |           |           |

| Con(high)                                                                                     | gn on-une                                                      | 50 Hz mains<br>60 Hz mains                             | 13.2      |               |           |           |

|                                                                                               |                                                                | 60 Hz mains                                            | 13.2      | 14.4          | 15.6      |           |

|                                                                                               |                                                                |                                                        | 44 0      |               |           | μS        |

|                                                                                               |                                                                |                                                        | 11.0      | 12.0          | 13.0      | μS        |

|                                                                                               |                                                                | high-frequency mode                                    |           |               | 10.1      |           |

|                                                                                               |                                                                | 50 Hz mains                                            | 8.8       | 9.6           | 10.4      | μS        |

| 0 ( ) ( ) ( )                                                                                 | o                                                              | 60 Hz mains                                            | 8.3       | 9.0           | 9.7       | μS        |

| Output short protect                                                                          |                                                                | T.                                                     | 22        | 40            | 40        |           |

|                                                                                               | gh off-time                                                    |                                                        | 32        | 40            | 48        | μs        |

| t <sub>det(sc)</sub> sh                                                                       | nort-circuit detection time                                    | 50 Hz mains                                            | 10        | -             | 20        | ms        |

|                                                                                               |                                                                | 60 Hz mains                                            | 8.3       | -             | 16.7      | ms        |

| Temperature protect                                                                           |                                                                |                                                        |           |               |           |           |

| ac                                                                                            | vertemperature protection<br>ctivation threshold<br>emperature | on-chip                                                | 160       | 175           | 190       | °C        |

| re                                                                                            | vertemperature protection<br>elease threshold<br>emperature    | on-chip                                                | 90        | 102           | 114       | °C        |

| Pin PWRDRV                                                                                    |                                                                |                                                        |           |               |           |           |

| V <sub>o(PWRDRV)</sub> ou                                                                     | utput voltage on pin                                           | high level                                             |           |               |           |           |

|                                                                                               | WRDRV                                                          | V <sub>VCC</sub> > V <sub>CC(low)</sub>                | -         | 10.7          | -         | V         |

|                                                                                               |                                                                | $V_{VCC} = V_{CC(stop)}$                               | -         | 8.5           | -         | V         |

| I <sub>source(PWRDRV)</sub> so                                                                | ource current on pin                                           | 20 μs maximum;                                         |           | -360          | _         | mA        |

|                                                                                               | WRDRV                                                          | $V_{PWRDRV} = 2 V$                                     |           |               |           |           |

|                                                                                               | nk current on pin<br>WRDRV                                     | 20 μs maximum;<br>V <sub>PWRDRV</sub> = 10 V           | -         | 900           | -         | mA        |

|                                                                                               |                                                                | 20 μs maximum;<br>V <sub>PWRDRV</sub> = 2 V            | -         | 260           | -         | mA        |

| Pin BLDRV                                                                                     |                                                                |                                                        |           |               |           |           |

|                                                                                               | utput voltage on pin                                           | high level                                             |           |               |           |           |

| В                                                                                             | LDRV                                                           | near mains zero<br>crossings                           | 0.92      | 0.95          | 1.00      | V         |

|                                                                                               |                                                                | strong bleeding                                        | 2.87      | 3.05          | 3.18      | V         |

|                                                                                               |                                                                | weak bleeding                                          | 1.8       | 1.9           | 2.0       | V         |

|                                                                                               | ource current on pin                                           | $V_{o(BLDRV)} = 0.25 \text{ V}$                        | -0.3      | -             | -0.9      | mA        |

| BI                                                                                            | LDRV                                                           | $V_{o(BLDRV)} = 0.95 V$                                | -1.2      | -             | -2.3      | mA        |

|                                                                                               |                                                                | $V_{o(BLDRV)} = 2.9 \text{ V}$                         | -3.9      | -4.4          | -4.9      | mA        |

| I <sub>sink(BLDRV)</sub> si                                                                   | nk current on pin BLDRV                                        | $V_{o(BLDRV)} = 0.4 V$                                 | 85        | 115           | 145       | μΑ        |

| Pin BLS                                                                                       |                                                                | •                                                      | '         | '             | 1         | '         |

|                                                                                               | egulation voltage on pin<br>LS                                 | dimmer detected                                        | -362      | -327          | -292      | mV        |

Silergy Corp.

#### Mains dimmable controller for LED lighting

Table 7. Characteristics ...continued

T<sub>amb</sub> = 25 °C; V<sub>CC</sub> = 19.5 V; all voltages are measured with respect to the ground pin; currents are positive when flowing into the IC; unless otherwise specified.

| Symbol                    | Parameter                   | Conditions                   | Min | Тур  | Max | Unit |

|---------------------------|-----------------------------|------------------------------|-----|------|-----|------|

| Pin RMAINS                |                             |                              |     | '    |     | 0,   |

| I <sub>i(RMAINS)</sub>    | input current on pin RMAINS | at top of mains sine wave    | 324 | 360  | 396 | μΑ   |

|                           |                             | for zero cross detection     | 18  | 22.5 | 27  | μА   |

| t <sub>d(mld)</sub>       | mains loss detection delay  | 50 Hz mains; no dimmer       | -   | 60   | -   | ms   |

|                           | time                        | 50 Hz mains; dimmer          | 80  | -    | 160 | ms   |

|                           |                             | 60 Hz mains; no dimmer       | -   | 50   | -   | ms   |

|                           |                             | 60 Hz mains; dimmer          | 67  | -    | 133 | ms   |

| I <sub>sink(RMAINS)</sub> | sink current on pin RMAINS  | V <sub>i(RMAINS)</sub> = 4 V | 400 | -    | -   | μА   |

<sup>[1]</sup> The peak voltage on pin DRAIN occurs each switching cycle, based 25,000 hours device lifetime.

## 12. Application information

Actual LED current values are slightly lower due to the IC supply current. If the AUX supply is unable to support the IC supply current, the control loop increases the low LED current limit.

Silergy Corp. SSL5301T

## Mains dimmable controller for LED lighting

Silergy Corp. SSL5301T

### Mains dimmable controller for LED lighting

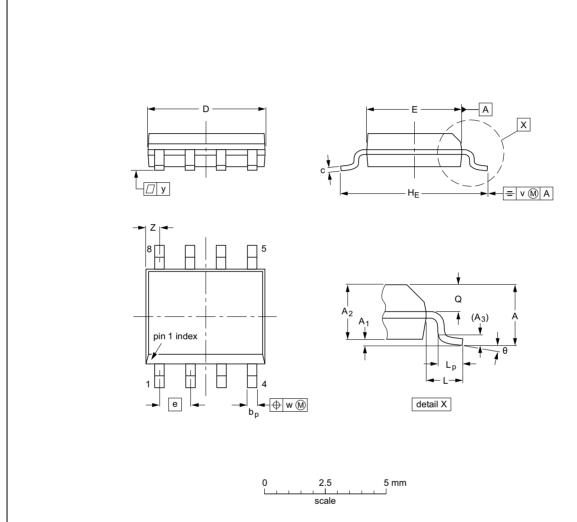

# 13. Package outline

#### SO8: plastic small outline package; 8 leads; body width 3.9 mm

SOT96-1

#### **DIMENSIONS** (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | С                | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE             | L     | Lp         | Q              | v    | w    | у     | z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|----------------|--------------|------------------|------------------|------------------|------|----------------|-------|------------|----------------|------|------|-------|------------------|----|

| mm     | 1.75      | 0.25<br>0.10   | 1.45<br>1.25   | 0.25           | 0.49<br>0.36 | 0.25<br>0.19     | 5.0<br>4.8       | 4.0<br>3.8       | 1.27 | 6.2<br>5.8     | 1.05  | 1.0<br>0.4 | 0.7<br>0.6     | 0.25 | 0.25 | 0.1   | 0.7<br>0.3       | 8° |

| inches | 0.069     | 0.010<br>0.004 | 0.057<br>0.049 | 0.01           |              | 0.0100<br>0.0075 | 0.20<br>0.19     | 0.16<br>0.15     | 0.05 | 0.244<br>0.228 | 0.041 | l          | 0.028<br>0.024 | 0.01 | 0.01 | 0.004 | 0.028<br>0.012   | 0° |

- 1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

|  | OUTLINE |        | REFER  | EUROPEAN | ISSUE DATE |            |                                 |

|--|---------|--------|--------|----------|------------|------------|---------------------------------|

|  | VERSION | IEC    | JEDEC  | JEITA    |            | PROJECTION | ISSUE DATE                      |

|  | SOT96-1 | 076E03 | MS-012 |          |            |            | <del>99-12-27</del><br>03-02-18 |

Fig 10. Package outline SOT96-1 (SO8)