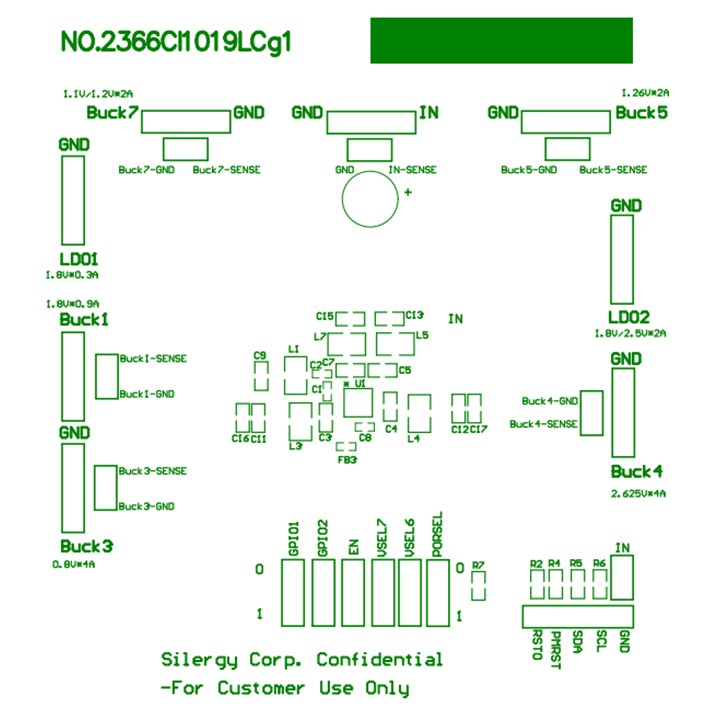

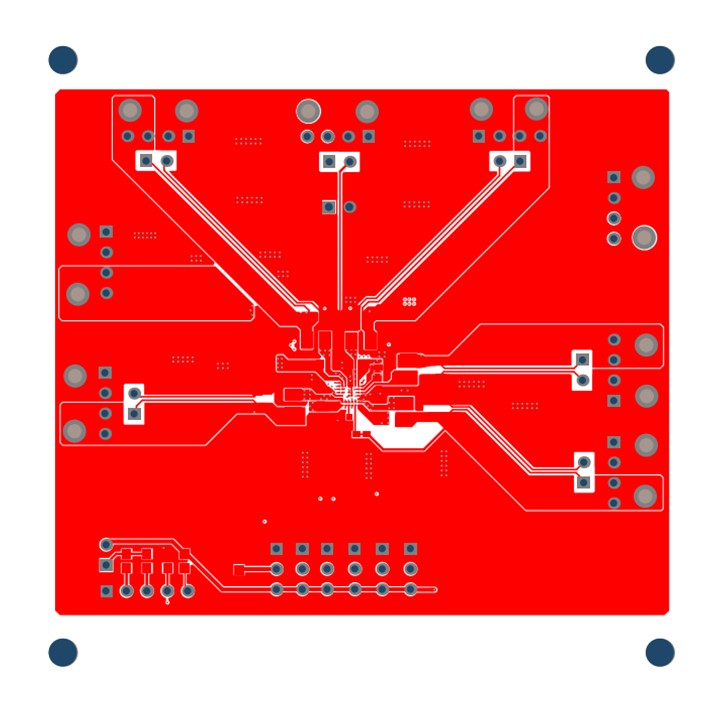

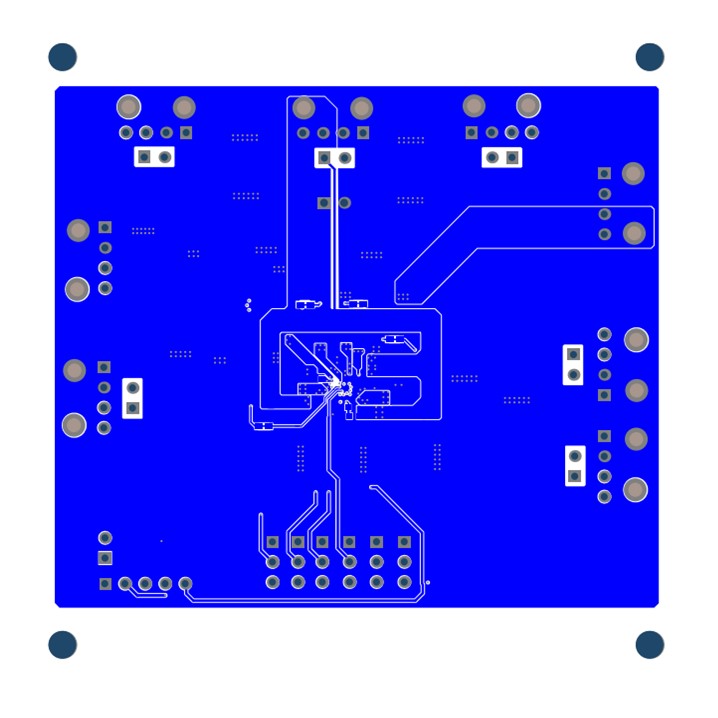

• 2.8V to 5.5V Input Voltage Range

• Channel 1 Synchronous Buck:

• Low RDS(ON) for Internal Switches (PFET/NFET): 150/150mΩ

• 0.9A Maximum Output Current Capability

• Default Output Voltage VOUT1 = 1.8V

• Channel 2 LDO1:

• 0.3A Output Current Capability

• Default Output Voltage VOUT2 = 1.8V

• Channel 3 Synchronous Buck:

• Low RDS(ON) for Internal Switches (PFET/NFET): 45/20mΩ

• 4.0A Maximum Output Current Capability

• Default Output Voltage VOUT3 = 0.9V

• 0.7V to 1.1V Programmable, 10mV Step

• Channel 4 Synchronous Buck:

• Low RDS(ON) for Internal Switches (PFET/NFET): 35/45mΩ

• 4.0A Maximum Output Current Capability

• Default Output Voltage VOUT4 = 3.15V Selected by PORSEL

• 2.3625V to 3.15V Programmable, 87.5mV Step

• Channel 5 Synchronous Buck:

• Low RDS(ON) for Internal Switches (PFET/NFET): 60/40mΩ

• 2.0A Output Current Capability

• Default Output Voltage VOUT5 = 1.2V

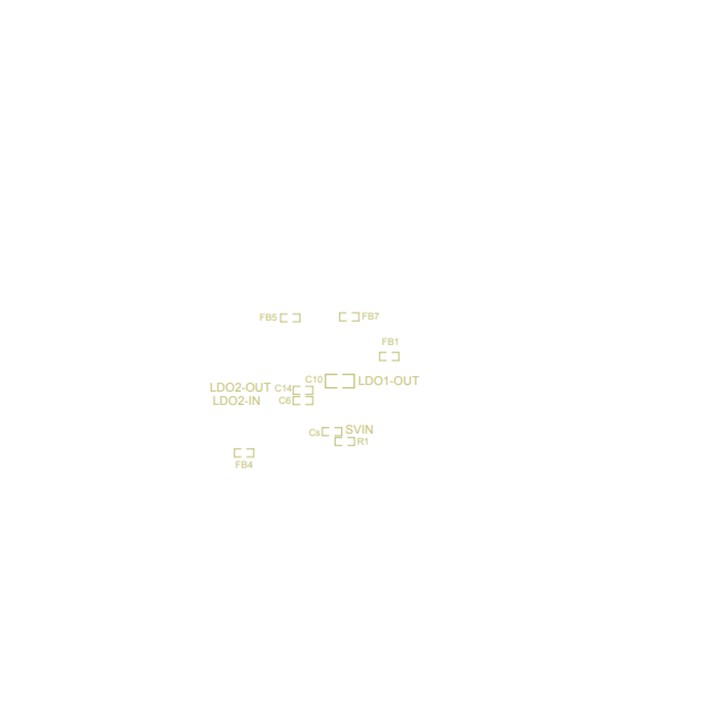

• Channel 6 LDO2:

• 0.3A Output Current Capability

• Default Output Voltage VOUT6 = 1.8V/2.5V Selected by VSEL6

• Channel 7 Synchronous Buck:

• Low RDS(ON) for Internal Switches (PFET/NFET): 60/40mΩ

• 2.0A Output Current Capability

• Default Output Voltage VOUT7 = 1.1V/1.2V Selected by VSEL7

• Reset Input/Output Function

• 2.0MHz Switching Frequency for Buck Converters

• Auto PWM/PFM Mode or Forced PWM Mode Controlled by I2C Interface

• I2C Interface up to 3.4MHz

• Output Voltage Level of CH3/CH4 Controlled by I2C Interface with DVS

• Dedicated Sleep Mode Controlled by GPIO1/GPIO2, PMRST

• Reliable Protections:

• Overvoltage Protection (OVP)

• Overcurrent Protection (OCP)

• Short-Circuit Protection (SCP)

• Overtemperature Protection (OTP)

• Compact package: CSP3.23×3.23-52 (0.4mm pitch)